Mô tả

After completion of this course learners will be able to:

(1) Understand the concepts design metrics which are to be optimized by a design engineer

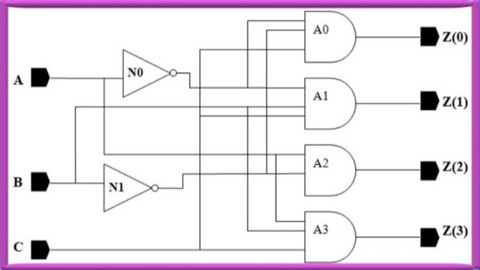

(2) Understand the concepts of IC design technology

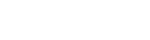

(3) Understand the implementation of logic using Fixed Function IC Technology, Full Custom ASIC Technology, and Semi-Custom ASIC Technology

(4) Understand the advantages and disadvantages of implementation of logic using Fixed Function IC Technology, Full Custom ASIC Technology, and Semi-Custom ASIC Technology

(5) Understand the concept of implementation of logic in PLDs

(6) Understand the concept of implementation of logic in FPGA

(7) Understand the IC design flow

(8) Understand the role of HDL in system design

(9) Understand the concepts of various Verilog language constructs

(10) Understand various operators and their uses in Verilog coding

(11) Understand how to use Xilinx software for writing a Verilog code

(12) Understand how to use Xilinx software for simulating a Verilog code

(13) Understand how to use Xilinx software for implementing a Verilog code

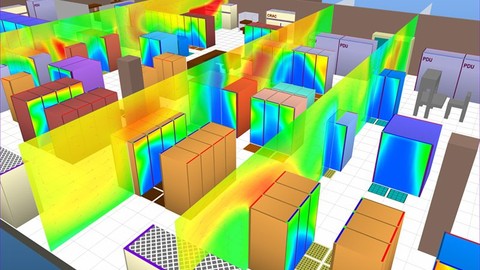

(14) Implement combinational logic by using behavioral modeling style

(15) Implement combinational logic by using dataflow modeling style

(16) Implement combinational logic by using structural modeling style

(17) Implement sequential logic by using behavioral modeling style

(18) Implement sequential logic by using dataflow modeling style

(19) Implement sequential logic by using structural modeling style

(20) Implement logic by using mos transistors

Bạn sẽ học được gì

Verilog coding for digital circuits

Yêu cầu

- No

Nội dung khoá học

Viết Bình Luận

Khoá học liên quan

Đăng ký get khoá học Udemy - Unica - Gitiho giá chỉ 50k!

Get khoá học giá rẻ ngay trước khi bị fix.

Đánh giá của học viên

Bình luận khách hàng